# **ST662A SERIES**

by T. Sampieri - Standard Circuits Marketing & F. Lentini - Standard Circuit Application

### DC-DC CONVERTER FOR FLASH MEMORY PROGRAMMING

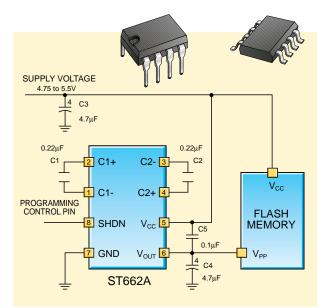

he ST662A is a compact, low cost 5V to 12V DC-DC converter IC that is ideal for generating the programming voltage required by industry standard dual voltage flash memories. The ST662A provides a stable 12V +/-5% output from a 5V +/-10% input and does not require an external inductor.

This device can supply 30mA of output current to drive the Vpp pin of the flash memory, even with an input voltage as low as 4.75V.

The ST662A has a low quiescent current of 100 $\mu$ A, while a logic controlled shutdown pin that can be directly driven by a microprocessor I/O pin, allows this to be reduced to only 1 $\mu$ A.

Available in compact DIP-8 and surface mounting SO-8 packages, the ST662A is offered in 0°C to 70°C and -40 to 85°C temperature ranges.

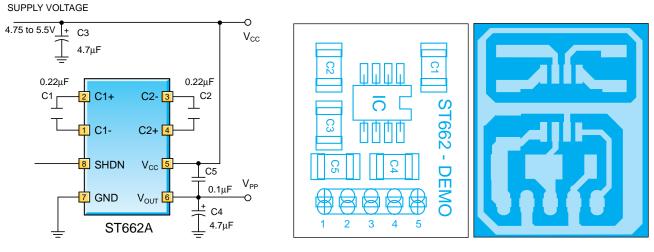

The device is supported by an application demoboard that can be used for evaluation. The printed circuit layout of the demoboard can be copied directly or incorporated into the customer's application board.

| DIP-8           | SO-8              |  |

|-----------------|-------------------|--|

| ST662ACN (Tube) | ST662ACD (Tube)   |  |

|                 | ST662ACD-TR (T&R) |  |

| ST662ABN (Tube) | ST662ABD (Tube)   |  |

|                 | ST662ABD-TR (T&R) |  |

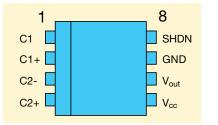

ST662A internal block diagram

#### DISCRETE AND STANDARD ICs GROUP

#### **FEATURES**

- > Output voltage: 12V +/- 5%

- Supply voltage range: 4.5V to 5.5V

- Guaranteed output current up to 30mA

- Very low quiescent current: 100mA

- > Logic-controlled electronic shut-down: 1mA

- > Only capacitors needed (no inductor)

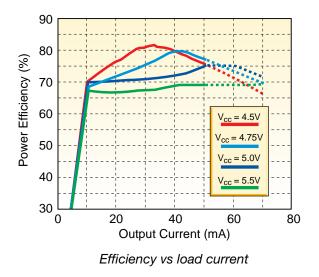

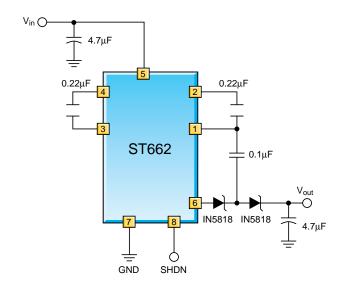

#### **APPLICATION CIRCUIT**

Based on fast charge/discharge of the capacitors, this circuit involves high di/dt values limited only by the Ron of switches. This implies a critical layout design due to the need to minimize inductive paths and place capacitors as close as possible to the device. In order to reduce noise a good layout is strongly recommended. For optimum performance, use very short connections to the capacitors and the values shown in the table of components. C3 and C4 must have a low ESR in order to minimise the output ripple. When using ceramic capacitors, their values can be reduced to  $2\mu$ F and  $1\mu$ F, respectively. If an aluminium electrolytic is chosen, they are 10µF or larger.

C5 must be placed as close to the device as possible and could be omitted if very low output noise performance is not required.

Typical application circuit

## TABLE OF COMPONENTS

| Capacitor      | Туре                    | Value µF |

|----------------|-------------------------|----------|

| Charge Pump C1 | Ceramic                 | 0.22     |

| Charge Pump C2 | Ceramic                 | 0.22     |

| Input C3       | Eletrolytic<br>Tantalum | 4.70     |

| Output C4      | Eletrolytic<br>Tantalum | 4.70     |

| Decoupling C5  | Ceramic                 | 0.10     |

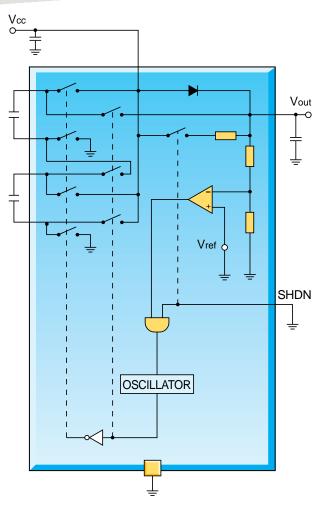

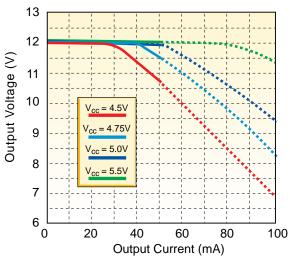

Output voltage vs output current

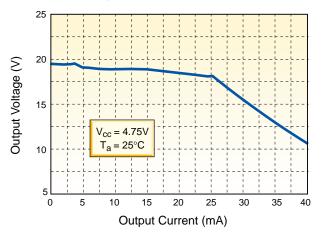

The output voltage depends on the output current in applications where the the output voltage is greater than 12V

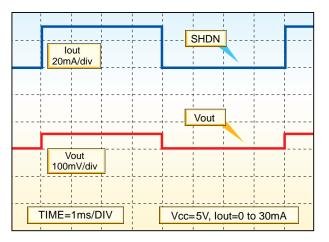

Load transient response

Evaluation kit circuit

DISCRETE AND STANDARD ICs GROUP

Evaluation circuit when  $V_{OUT}$  is greater than 12V

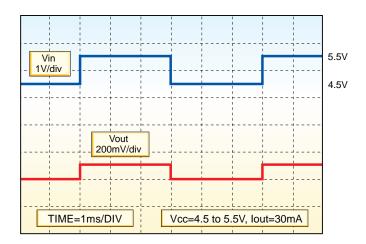

Line transient response

Printed demoboard